7系列FPGA GTX/GTH 收发器用户指南说明 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

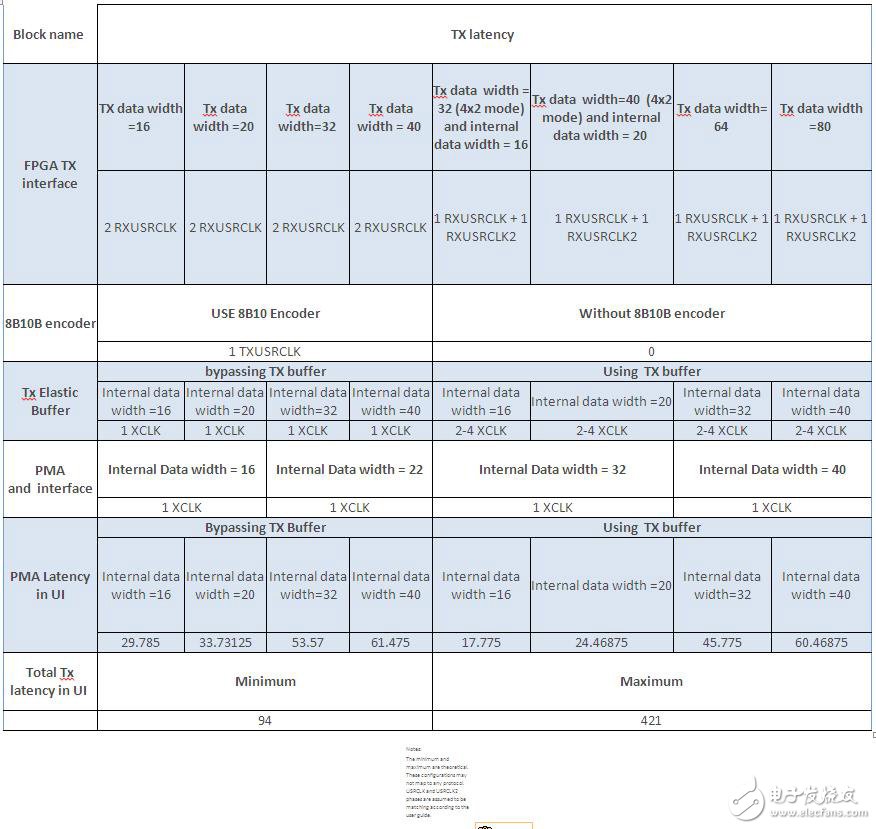

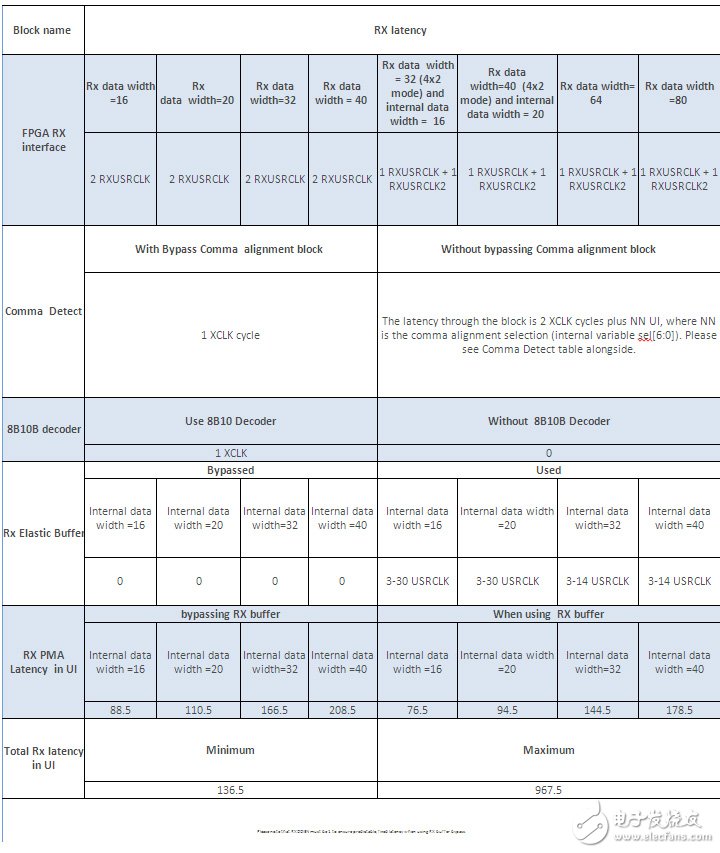

本文提供用于 7 系列 FPGA GTX 收发器的 TX 和 RX 时延值。这些表将被添加到 7 系列 FPGA GTX/GTH 收发器用户指南 (UG476)。

注:

1. 最低和最高为理论值。这些配置可能不会映射到任何协议。USRCLK 和 USRCLK2 相位假定为根据用户指南匹配。

2. TX 时延表上有打字错误。时延体现为 RXUSRCLK 周期,但应该是 TXUSRCLK。

注意:请注意,RXDDIEN 必须为 1,这才能确保使用 RX 缓冲旁通时有可预见的固定时延。

注 1: 通过 TX 架构接口的时延会取决于时延的精确定义。如果时延定义为从把数据放在 TXDATA 上的时钟边缘到离开Fabric接口(PCS 内部)数据第一部分计时的时钟边缘,那么上表中的项目就是准确的,忽略从Fabric到 GT 的时钟插入时间。

注 2: 离开复位时,通过弹性缓冲的时延为:

2 RXUSRCLK cycles

+ CLK_COR_MIN_LAT byte TImes

+/- 0.5 RXUSRCLK cycles

查看评论 回复