基于LV FPGA设计滤波器步骤详解 - FPGA/ASIC技术 -

对于NI很多专注于数据采集领域的客户来说,对采集到的信号在前端加入滤波功能是非常常见的需求。但是,可能由于他们对NI产品不够了解,不知道这部分功能完全可以由FPGA来完成,从而让NI错失应有的订单和机会。例如,客户原本的系统构建是在传感器与NI cDAQ之间再外加滤波电路。明了这个需求以后,我们完全可以向客户推荐具有FPGA终端的cRIO,这样的解决方案即简化了客户的系统构建方案,同时帮NI增加了销售额,两全其美!那么问题就来了,我们要如何在LV FPGA中实现一个靠谱的滤波器功能呢?

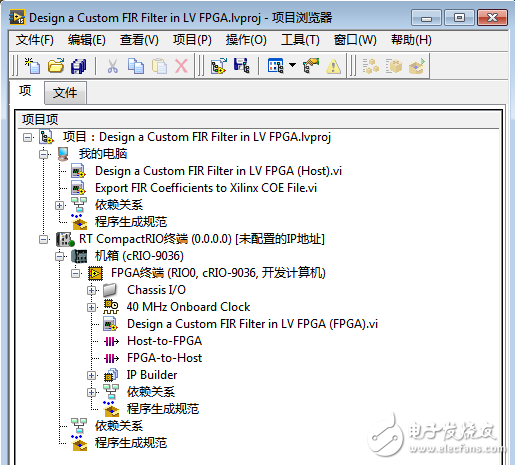

第一步:创建项目

创建任何一个具有FPGA终端的设备和LV 项目。本文中利用cRIO 9036为例。注:本文中所有内容均可以利用仿真模式实现,包括FPGA中的滤波器算法,读者可以在没有硬件资源的情况下模拟本文中的操作。实际体会IP CORE的使用。

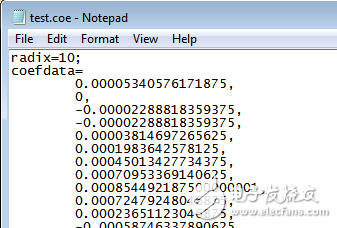

第二步:生成滤波器系数文件“.coe”

在LabVIEW范例查找器中搜索:coe。并将:Export FIR Coefficients to Xilinx COE File.vi添加至项目的“我的电脑”终端下方,以待后续使用。(Coe是指coefficient,也就是系数。在Xilinx FIR滤波器中分为很多阶数,每一阶都对应一个系数。所以这个文件是用来存放滤波器系数的。)

这个vi的作用是用于后续生成Xilinx IP Core的配置过程中所需要用到的一个系数文件,其中的系数定义了滤波器的通带,阻带和采样率等信息。

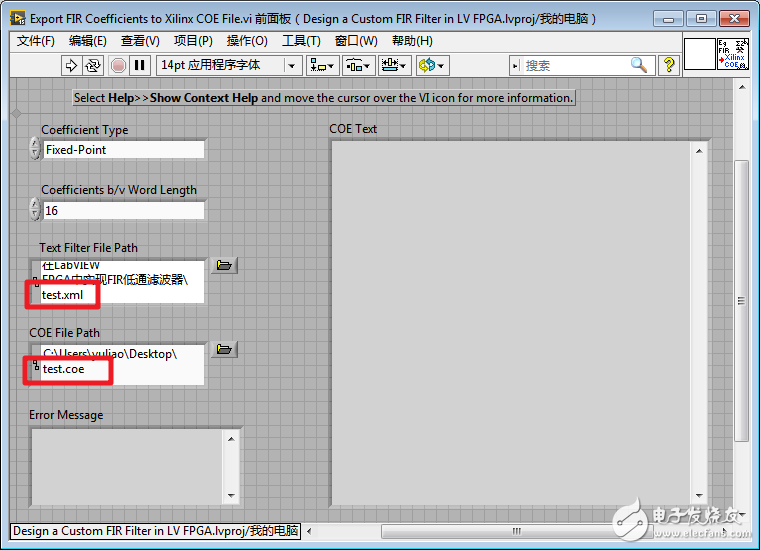

打开这个vi,可以看到前面板上需要配置相关的使用信息,红圈圈出的两个部分是vi正常运行的必须文件,刚开始使用的时候,读者只需要在操作系统中创建两个空白的文件就可以了。

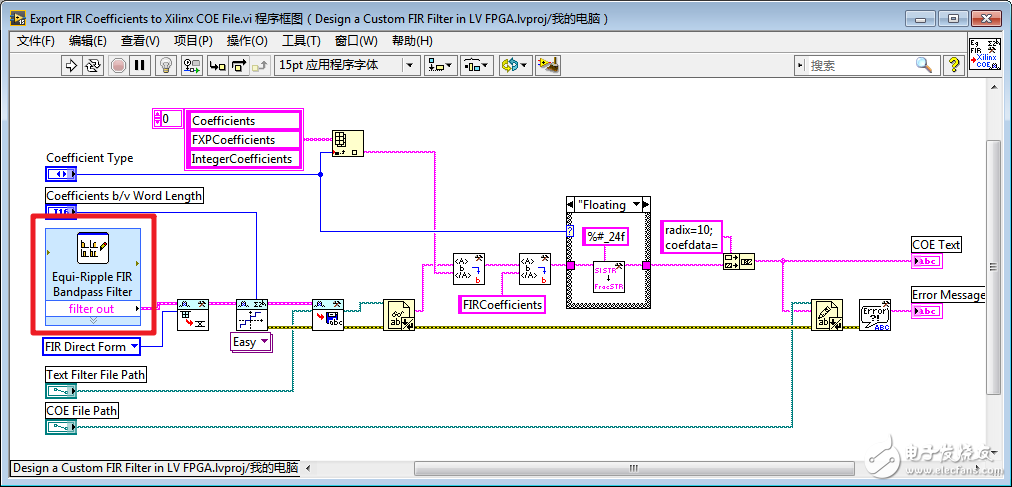

切换到程序框图,并双击打开红圈处的Express VI,它的作用是帮助用户快速设计滤波器。

Express VI配置界面:

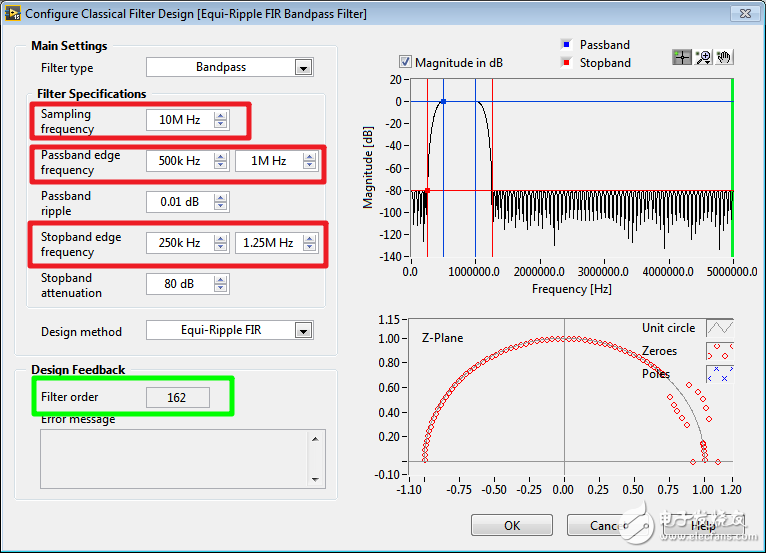

在这个界面里,需要对滤波器的采样率,通带信息,阻带信息等进行配置。本文以一个通带为500kHz~1MHz,阻带为0~250kHz,1.25MHz以上的滤波器为例。红圈中显示配置相关信息,绿圈中为生成滤波器的阶数也是系数个数。右边两幅图是所配置滤波器的频域响应图和零点极点分布图。完成配置后,运行该vi,会生成一个coe文件,可用记事本打开,看到里面有生成的滤波器系数。以待后续使用。

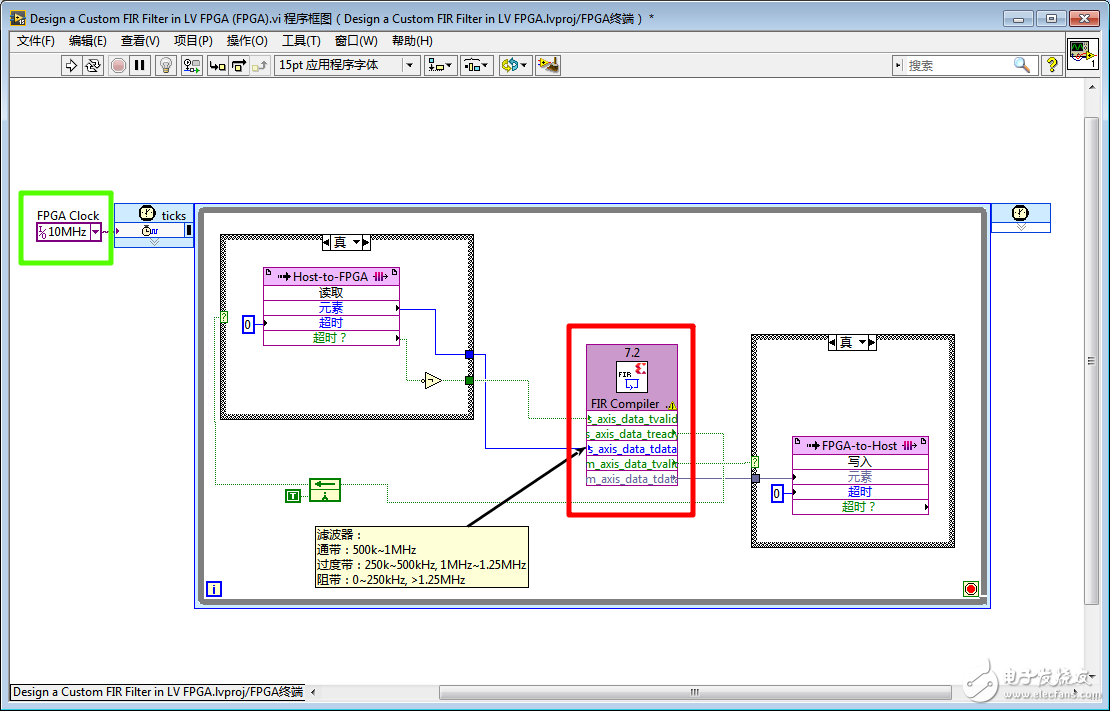

第三步:在LV FPGA中配置及使用Xilinx FIR滤波器IP Core

创建如图所示的两个FIFO,用于将滤波前的数据传给FPGA,将滤波后的数据传回给上位机。

下图中所示为本项目中的FPGA程序,红圈处为本文的主角:Xilinx FIR IP Core。可以看到,图中所示为7.2版本,因为此硬件中使用的是Xilinx K7系列FPGA,若为V5系列FPGA,程序中为5.0版本。配置和使用大同小异,本文不再赘述。绿圈处是SCTL的循环时钟源,推荐配置为与滤波器采样频率一致,简化后续使用。

图中FIFO与IP CORE的数据传输由“四线握手”实现有效数据的顺利传输,可参阅相关文档。

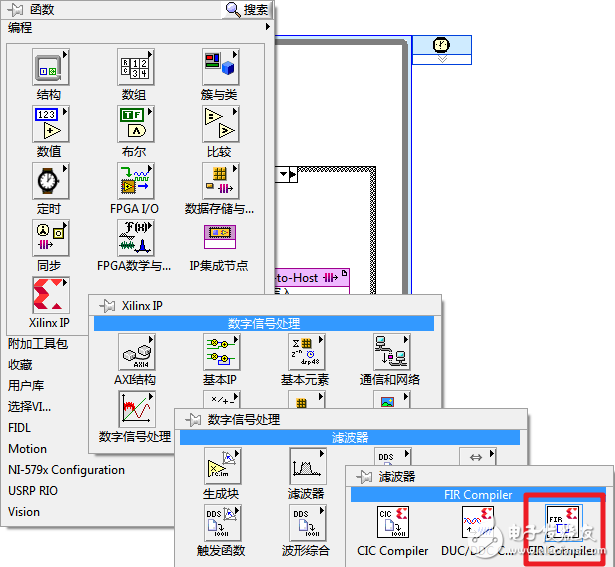

在下图所示位置可以找到Xilinx FIR IP Core

放到程序框图上后,双击对其进行配置。

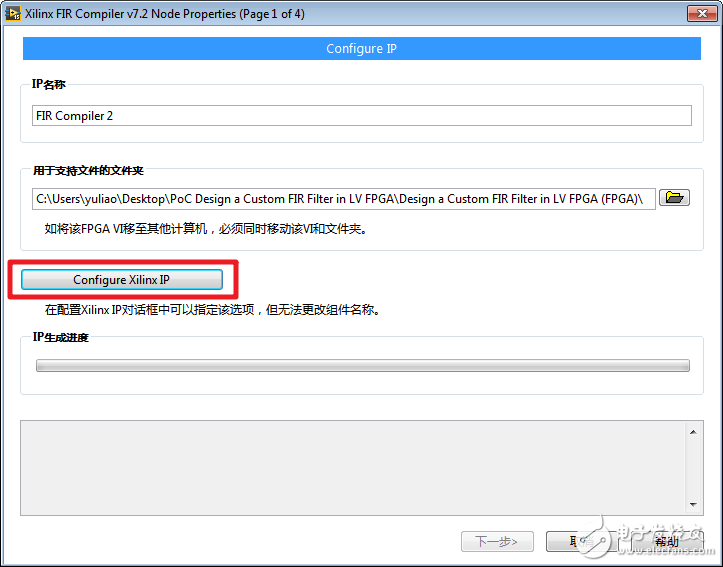

点击Configure Xilinx IP,会打开Xilinx Vivado Customize IP环境。对滤波器进行配置

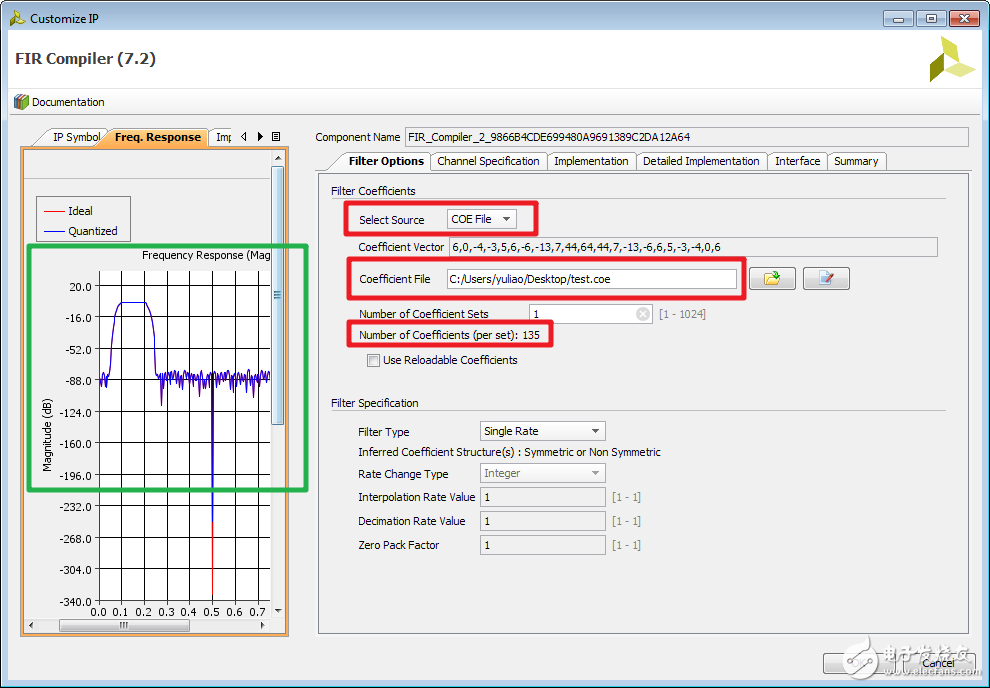

1)在Filter OpTIons中,选择在第二步中生成的coe文件,vivado会自动加载文件内部信息。红圈处显示检测到的系数个数,左侧Frequency Response窗口中显示滤波器的频率响应。

查看评论 回复