֧��25G/28G�������� FPGAʵ��TB������Ӧ��ͻ�� - FPGA/ASIC����

��������ǰIEEE�����ָ����2015��ͨѶ����Ĵ�������Ҫ��1Tbit/s����2020�������֧�ֵ�10Tbit/s�� �ñ��滹ָ����2015��������ж�����װ�����������һ����ʮ��̨�����л����������Ի���(M2M)�Ļ������ڹ������(OTN)Ӧ�÷��棬���Ľڵ��ÿ����������2015��Ԥ�ƴﵽ100G?400G������2020�����������400G��1T��

����FPGA������1Tbit/sӦ��

Ϊ������TB��������Ӧ�ã��г����Ƴ�UltraScale All Programmable�ֳ��ɱ��������(FPGA)���������֧��1Tbit/sϵͳ�Ľ��ã��Ҿ�����Ч�ܡ�ϵͳ���϶Ⱥߴ������㷺����������ͨѶ�����⡢����������������ĵȸ���Ӧ�á�

��ʵ�����˾���ѱ�ʾ��1TB����Ӧ�õ�����ϣ���շ�����ֱ������25G/28G���壬�������������(Routability)������(Crosstalk)���ʽ�������(DifferenTIal InserTIon Loss)���迹ƥ��(Impedance Matching)�����⡣

�¿�FPGA���Կ˷��������⣬������ʹ�ø�λʱ���������ṩ25G/28G�����������һ��֧�ָ���1Tbit/sӦ�á�

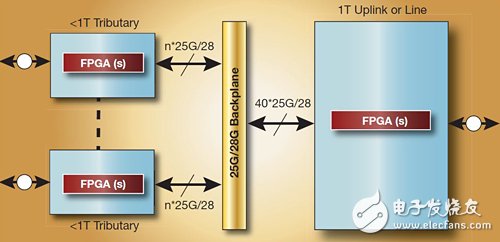

ͼ1���ڸ߲��TB��ϵͳ����ͼ�У��������1Tbit/s��֧·����һ��1Tbit/s���߿�����Ѷ�Ŵ��䡣

ͼ1��ͨ�õ�1Tbit/sϵͳ�߲��ģ��ͼ�����У������������1TB��֧·��(ͼ1��������)����������Ϊ25G/28G�ı�����һ��1T�߿������� ͼ2��3��4��Ϊ����1Tbit/s��̫�����OTN����Ӧ�õ�ģ��ͼ��ȫ��������FPGAΪ������

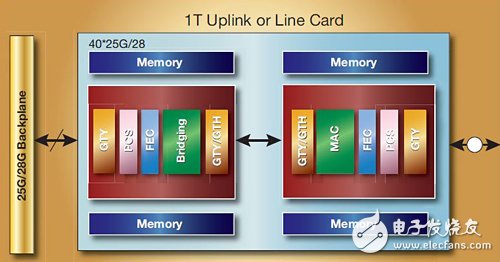

ͼ2���������1Tbit/s����̫����֧·����25G�������Ӷ�1TB��̫����������ģ�鴫��Ѷ�š�

25G�����շ���սʤ�ɲ���������

��������ģ��ͼ�����˽⣬��û��֧��25G/28G�ı����շ�����������ʵ�ָ���1T����Ӧ�á�����ֻ��һ�����߱�10G����ı��壬�����������ԡ��������ʽ������ģ��������迹ƥ������⡣

�ɲ���������

��Щʵ��չʾ���ܴ���Ϊ40&TImes;25Gbit/s =1Tbit/s�����ʣ���25G/28G���������е���ʮ��ͨ����������ͨ��Լ0.25Ӣ��������Ҫȡ�����������أ�������ѹװ�Ļ�е��֧�ֶ��ͨ��·�ɵ�����

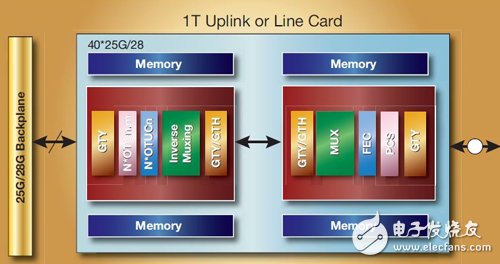

ͼ3��1TB��̫����������ģ����OTN�����Ϸֲ���Ч�ظ�����25G/28G���������ظ�ʹ�ü��е�OTN�߿�(<1Tb)��

������ӿڽ�֧��10Gbit/s��������ͨ��������Ҫ���ӵ�ԭ����2.5����ÿ��1Tbit/s�߿���֧·��ı���ͨ�����������ʮ�����ӵ�һ�ٸ�������Ҫ��ʮ���֧·����߿���ϵͳ�У����������ͨ��������Ϊ100&TImes;25=2,500����Ϊ·����ɺܴ�����⡣

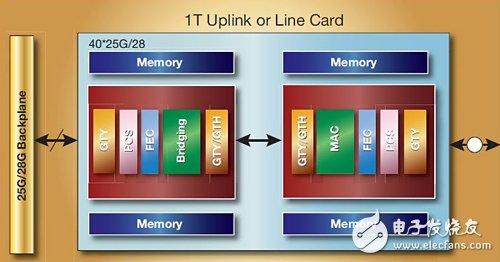

ͼ4��1TB OTN�߿���28G���������ظ�ʹ�ôӵ���1TB OTN֧·ģ�鴫�͵�Ѷ�š�

ʹ�ñ��������ʱ����Megtron-6Ϊ�������糣��ԼΪ3.65�ұ����߿���Ϊ7mil��ʹ���ᷢ��ÿ���ʽ��״�߶ԵĶ�ջ�߶�Ϊ��ÿ100��ķ(Ω)�IJ��ģ�迹��Ӧ16mil��

���豳�����������ͨ����2����(mm)������ÿ�������������ż���Խ���һ��ͨ������ˣ�����ÿ���ܹ���ÿ��������֧��ʮ��ͨ��(����+����)����ҵ��

�����25Gbit/s������������ͨ����Ҫʮ�������߲㣬�����ܺ��Ϊ16mil×16���߲�=0.256Ӣ���������10Gbit/s���������ʣ�����Ϊ0.640Ӣ��(16×2.5=40���߲㣬�����ܺ��Ϊ16mil×40��=0.640Ӣ��)��

���ǣ����������ͨ����ͨ·������Ⱦ���������ͨ·��ֱ��Ϊ15mil���������Ϊ25:1����������������ԼΪ 14×25=350mil����ˣ�10G������֧��1TӦ�á�

��������������������������

�鿴���� �ظ�

"֧��25G/28G�������� FPGAʵ��TB������Ӧ��ͻ�� - FPGA/ASIC����"���������

��������

- Xilinx FPGA�ڻ���������е����� - FPGA/ASIC���� -

- ����CPU���ģ������д

- ����FPGAоƬ�Ĺ��£���֪�������أ� - �ɱ���� -

- Mellanox����Ƕ��Xilinx FPGA,��ʵ�����繦������ -

- ��˼�Ƽ���������Cortex-A76��Mali-G76���������ڵ�Ar

- ����˼�뵼���Ƴ�ȫ�µ�ģ�黯IP�ˣ���Ϊ�ͻ��ṩ����

- FPGA��Ʒ��������������˼����ս�����������г����� -

- ����FPGA�����ѧϰ�Ĺ�ϵ̽����� - �ɱ���� -

- ���ΪAI�����ޣ�������FPGAΪ����֧�� - �ɱ����

- SDSoc��������-ʹ��MIO����LED - �ɱ���� -