有杰出电源抑制性能的低静态电流LDO【ADI】 - 模拟电源 -

北京2011年2月16日电 -- Analog Devices, Inc. (ADI),全球领先的高性能信号处理解决方案供应商,最近推出两款具有杰出电源抑制性能的低静态电流 LDO(低压差线性调节器)ADP124 和 ADP125,有助于电池供电的便携式设备更长久、更高效地工作。两款 LDO 新品在100kHz 时均具有 60dB 的出色 PSRR(电源抑制比)性能,这是最接近的竞争产品的两倍;并且在 1.8V 输出时可实现 35Vrms 的低噪声性能。新款 LDO 的输入电压范围为 2.3V 至 5.5V,输出电流最高可达 500mA,输出电压最低为 0.8V,静态电流低至 210μA,500mA 负载时的电压差为 130mV,这些特性能够进一步提高便携式设备在宽输入电压范围内的工作效率。

ADI 公司电源管理部产品线经理 Walt Heinzer 表示:“为了获得最佳的混合信号处理性能,设计便携式产品时要求解决方案尺寸要小、功耗低并具有高电源抑制比,特别是在电源为隐蔽噪声源的情况下。这些高性能 LDO 可提供 60dB 的出色 PSRR,与提供 25dB 或 30dB PSRR 的普通 LDO 相比,性能提高 30dB,从对数意义上说则是提高30倍。新款 LDO 以极具竞争力的价格实现了极低压差、低噪声和高电源抑制比的最佳组合,从而超越了其它竞争产品。”

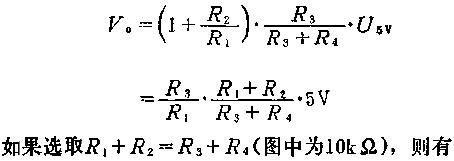

ADP124 提供 1.75V 至 3.3V 范围内的31种固定输出电压选项。ADP125 LDO 利用外部分压器提供 0.8V 至 5.0V 范围内的可调输出电压。两款器件经过专门设计,利用 1μF 小陶瓷输入和输出电容便可稳定工作,适合高性能、空间受限应用的要求。这些 LDO 采用紧凑型 2mm x 2mm x 0.55mm LFCSP 封装或8引脚裸露焊盘 MSOP 封装。

主要特性和优势

100kHz 时 PSRR 为 60dB,防止较高频率混入 RF(射频)负载,从而提高相位噪声性能。

初始精度为1%,能够为 FPGA 应用中的内核电压轨提供极小的容差。

500mA 时电压差仅为 130mV,功率损失极小,并允许设备在电池放电曲线以下的范围工作。

1.8V 输出时噪声低至 35VRMS,能够为高性能模数转换器提供干净的电源,而无需添加额外的输出旁路电容。

在 1F 陶瓷输出电容下稳定工作,尺寸紧凑,适合空间受限的应用。

查看评论 回复