小数分频与快锁芯片ADF4193的原理与应用 - 模拟电源 -

0引言

在数字移动通信系统的设计过程中,经常采用跳频方法来提高通信系统的抗干扰、抗多径衰落能力。但这要求快速跳频系统中的超快速跳频PLL能够在几十微秒(μs)内稳定到所要求的相位和频率。为达到这个要求,可采用"乒乓"体系结构。但这种结构需要两个频率合成器。其中当一个频率合成器作为LO工作时.另一个频率合成器的作用是锁定下一步要求的频率。而现在。也可以用一个快锁芯片来实现。美国ADI公司生产的ADF4193快速开关频率合成器就是采用一个PLL的快锁芯片。它能满足"乒乓"结构的切换指标,故可用在无线发射机和接收机的上变频和下变频电路的LO电路中。

1 ADF4193的特点和PLL工作原理

ADF4193是基于小数分频的快锁芯片。该芯片的主要特点如下:

◇具有快速调整的小数-N锁相环结构;

◇可用单片锁相环代替开关式合成器;

◇可在GSM频带内实现5μs跳频,并可在20μs内使相位稳定;

◇2 GHz输出时具有0.5级的相位误差;

◇可编程输出相位;

◇射频输入范围可达3.5 GHz;

◇带有3线串行接口;

◇芯片内置低噪声差动放大器;

◇其相位噪声灵敏度可达-216 dBc/Hz。

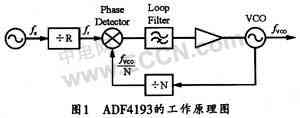

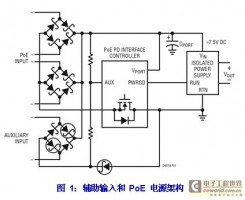

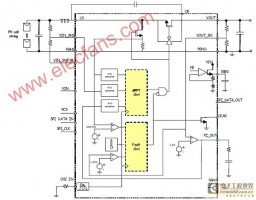

ADF4193主要是基于"乒乓"体系结构的跳频原理。ADF4193的工作原理如图1所示,图中,VCO的作用是提供一个参考频率fx,fx经过预分频R得到鉴相器输入端的参考频率,图1中的环路滤波器的作用是滤除鉴相器输出信号的高频成分和噪声,并将鉴相器的输出电流转化为电压送到VCO的输入端。以控制VCO的输出频率。同时将VCO输出频率经过N分频后反馈给鉴相器。鉴相器的作用是对反馈频率和参考鉴相频率进行比较,当鉴相器两个输入信号的相位同步(且fvco/N=fr)时,VCO的输出频率就是要锁定的频率。