allegro使二条时钟线等长的方法 -

[导读] 为了使二个SDRAM的时钟线等长,我查阅了很多资料,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通过延时处理达到等长的目的。 首先是我们先要为想要等长的线找一个精

为了使二个SDRAM的时钟线等长,我查阅了很多资料,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通过延时处理达到等长的目的。

本文引用地址: http://www.21ic.com/app/eda/200905/42928.htm

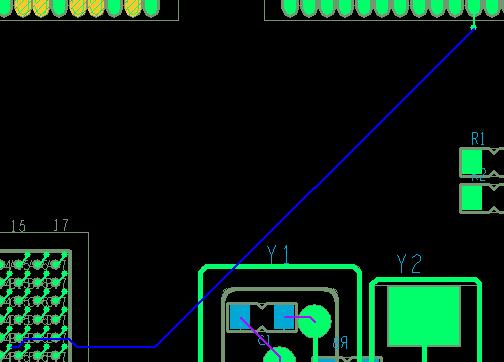

首先是我们先要为想要等长的线找一个精确的数据,为此,我先布设了最长的那条时钟线

然后,通过display-->element查看他的长度,可以看到:

Netpathlength:1113.48MIL

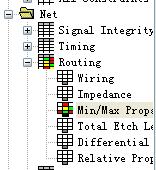

这就是我们参考的长度,也可以在下面的约束管理器中看到这个值,接着我们打开约束管理器,通过打开约束管理器,在

注意图中带颜色部分,可以在右边到所有的网络

在你想等长的网络名称上右键鼠标,选择创建一个引脚对

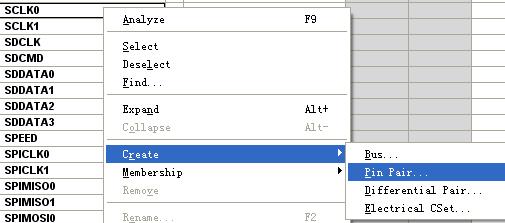

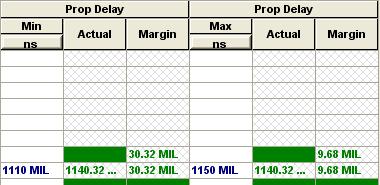

然后在右边输入最大和最小的值,如图

我的最小值是1110MIL,最大值是1150MIL,参照着最长那条时钟线设置的

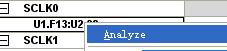

此时,在时钟网络名称上右键并选择Analyze

我们就会看到这个效果

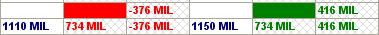

这个图中绿色部分就是你已经布的时钟线的长度,如果他不在范围内就会显示为红色

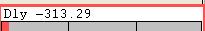

也就是我们的还离最小值差距376mil,怎么办呢?下面到了手动延时或者叫延长操作了

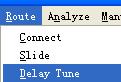

启动Route-->DelayTune

设置一下右边属性

在另一条短的时钟线上,开始拖出一些回形的走线来

右边如果是显示为红色

那就继续变换的拖动,更变大小,直到红色部分变为绿色

那就完成了等长设置.

查看评论 回复