基于Andes Core 的 ESL 解决方案――AndESLive -

[导读]

近年来,IC 设计正在向电子系统级(ESL,electronic system level)解决方案发展。多家 EDA 公司以及 IP 供应商都推出了各自的 ESL 开发工具。晶心科技(Andes technology)是亚洲首家完全自主知识产权 32 位嵌入式处理器 IP 核(即 Andes core)的供应商与系统芯片开发平台的设计公司。晶心科技为基于 Andes core 进行 SoC 设计和开发的客户提

本文引用地址: http://www.21ic.com/app/eda/201807/797178.htm

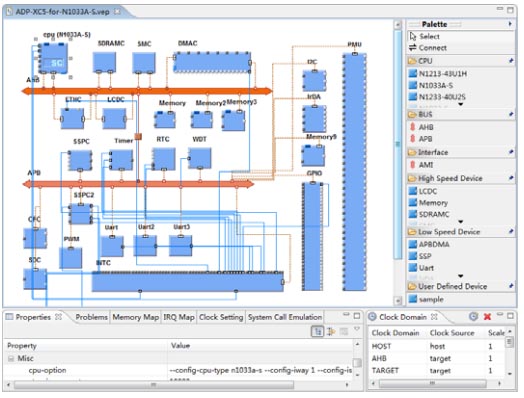

供了一套完整的 ESL 解决方案-AndESLive。本文将介绍 AndESLive 这套 ESL 开发工具是如何帮助客户快速确定符合市场需求的最佳体系结构,并实现软硬件并行工作以缩减开发周期的目的。1. 为什么采用 ESL 设计 随着 SoC 设计的发展,芯片规模变得越来越大,IP 的使用进一步增加,复杂度和性能的需求不断提高。另一方面,嵌入式软件开发在整个设计中所占的比重也越来越大,整个系统的性能越来越取决于软硬件协同工作所表现出的综合性能。因此,芯片在设计阶段就需要进行深入的系统级仿真,以及在芯片的仿真模型上运行大量软件以覆盖所需的功能。传统的设计流程无法满足这些仿真的执行性能,就需要采用一种新的工具来避免由于早期设计的不确定性所带来的影响。 ESL 设计和验证是一种在较高的抽象层次上对芯片进行描述和分析的设计方法学,它能够让设计工程师快速地构建原型平台,并以紧耦合的方式开发、优化和验证复杂系统架构,从而实现最优化的系统性能。另外,采用 ESL 的方法还可以使软件设计人员提早进入调式和验证,大幅缩短产品上市时间。因此,采用 ESL 的设计方法已经成为IC 设计的必然趋势。2. 晶心科技的 ESL 解决方案:AndESLive AndESLive 是以 ESL 设计和验证理念为理论基础,专门针对基于 Andes core IP 进行 SoC 开发而设计的 ESL 开发工具。它集成在 AndeSight(晶心科技基于 Andes core 的集成开发环境)中,并通过 AndeSight 提供的 GUI 界面和工程师进行交互。AndESLive 为设计人员提供了一个虚拟评估平台(VEP,Virtual Evaluation Platform),它是一个描述真实系统行为的系统级仿真模型。VEP 的核心由两个部分组成,前端叫做Virtual SoC Builder,它可以帮助设计人员快速构建系统原型平台;后端是一个系统级的模拟器。工程师可以在原型平台上,对系统(包括硬件和软件)性能进行评估和验证,从而实现系统设计的最优化。3. Virtual SoC Builder AndESLive 中的 Virtual SoC Builder 为设计人员提供快速搭建目标系统原型的功能。在 AndESLive 中,已经预定义了 Andes 各个系列 CPU 的 IP,以及各种周边设备控制器的 IP,包括高速设备(Memory、DMA、LCD、Ethernet 等)、低速设备(Uart、GPIO、SSP 等)和 BUS(AHB、APB)。另外,工程师还可以添加用户自定义的 IP 模块来实现一些特殊的功能需求。 图 1 为 Virtual SoC Builder 在 AndESLive 中的基本 UI 界面。界面上方的区域是设计人员构建虚拟 SoC 系统模型的编辑区,工程师根据需要通过选择右侧 IP 库中的 IP 模型,并将它们之间的端口(主从端口和读写端口)进行连接,就可以很快的架设起初步的SoC 原型。工程师可以通过 Virtual SoC Builder 界面下方的 Properties 视窗对单个 IP 模块的属性进行配置,例如修改 CPU 的 I/D Cache、MMU、I/D Local memory 等参数。还可以通过其他一些视窗对整个 SoC 系统进行设定,例如配置内存映射、配置中断和设置时钟等。

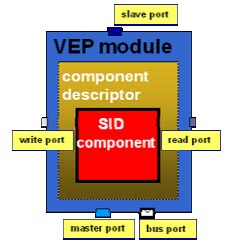

图 1、Virtual SoC Builder 操作界面4. AndESLive 中的模拟器4.1 基于 SID 的模?器 AndESLive 采用 SID 作为 VEP 的后端模拟器来实现系统级仿真的功能。SID 是一个用于构建计算机系统仿真的框架,是一个松耦合模拟组件的集合。VEP 中的各种 IP 模块都是 SID 的组件,SID 通过标准的 API(定义管脚、总线、属性和关系)挂载组件,并通过 SID 配置文件实现组件间的连接和交互,从而达到模拟物理硬件行为的目的。AndESLive 中的模拟器具有很高的仿真效能,其执行是基于机器周期或是机器指令的。工程师不仅可以在 VEP 上实现应用程序的快速执行,还可以进行可视化的程序调试和分析(profiling)。另外,模拟器提供了多种模拟 I/O 设备,例如 LCD、Uart、GPIO、RTC 等,这使得工程师在 VEP 上运行应用程序时可以进行模拟的输入或者得到与真实硬件平台一样的输出结果。4.2 VEP中的IP模型 事物处理级模型(TLM)用于建模可执行平台,通常只描述系统各个功能单元之间的抽象操作,一般来说即指各个功能单元之间交换的整个数据结构(或对象)上读取/写入或发送/接收操作。 AndESLive 的 VEP 功能就是基于事务级建模方法,采用事物处理级模型。VEP 中虚拟 IP 模型的实现由两部分组成,内部是标准的 SID 组件,外部是符合 VEP 建模标准的组件描述符,如图 2 所示。组件描述符定义了 IP 功能模块在 AndESLive 中需要展现的特性,例如总线、管脚以及事件、时序等各种属性,通过这层包装 SID 组件便可以加入到 VEP 中。对于 AndESLive 中已经预定义好的 IP 模块,工程师只要通过修改这些 IP模块的描述符,改变模块的参数和属性,便可以使之具备所需要的新的特性。

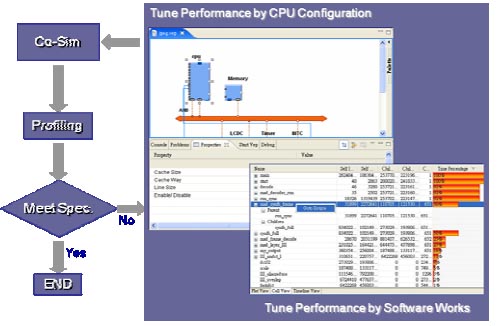

图 1、Virtual SoC Builder 操作界面4. AndESLive 中的模拟器4.1 基于 SID 的模?器 AndESLive 采用 SID 作为 VEP 的后端模拟器来实现系统级仿真的功能。SID 是一个用于构建计算机系统仿真的框架,是一个松耦合模拟组件的集合。VEP 中的各种 IP 模块都是 SID 的组件,SID 通过标准的 API(定义管脚、总线、属性和关系)挂载组件,并通过 SID 配置文件实现组件间的连接和交互,从而达到模拟物理硬件行为的目的。AndESLive 中的模拟器具有很高的仿真效能,其执行是基于机器周期或是机器指令的。工程师不仅可以在 VEP 上实现应用程序的快速执行,还可以进行可视化的程序调试和分析(profiling)。另外,模拟器提供了多种模拟 I/O 设备,例如 LCD、Uart、GPIO、RTC 等,这使得工程师在 VEP 上运行应用程序时可以进行模拟的输入或者得到与真实硬件平台一样的输出结果。4.2 VEP中的IP模型 事物处理级模型(TLM)用于建模可执行平台,通常只描述系统各个功能单元之间的抽象操作,一般来说即指各个功能单元之间交换的整个数据结构(或对象)上读取/写入或发送/接收操作。 AndESLive 的 VEP 功能就是基于事务级建模方法,采用事物处理级模型。VEP 中虚拟 IP 模型的实现由两部分组成,内部是标准的 SID 组件,外部是符合 VEP 建模标准的组件描述符,如图 2 所示。组件描述符定义了 IP 功能模块在 AndESLive 中需要展现的特性,例如总线、管脚以及事件、时序等各种属性,通过这层包装 SID 组件便可以加入到 VEP 中。对于 AndESLive 中已经预定义好的 IP 模块,工程师只要通过修改这些 IP模块的描述符,改变模块的参数和属性,便可以使之具备所需要的新的特性。 图 2 VEP 模型结构图 如果需要添加新的 VEP 模块,工程师需要进行 VEP 模型的建模。建模有两种方式,如果 SID 组件是由 C/C++语言来描述,那组件外部需要一层 XML 语言实现的描述符来进行包装;如果工程师希望用 SystemC 实现模块,则需要实现一个 SID-SystemC 桥文件,用 来 完 成 SID 与 SystemC 接 口 之 间 的 通 信 功 能 。 对 于 编 写 组 件 描 述 符 文 件 或 者SID-SystemC 桥文件,晶心科技会提供完整的培训和技术资源,帮助客户快速实现建模工作。5.使用 AndESLive 进行设计和开发5.1 探索最优化的系?架构 随着 SoC 芯片规模扩大、工艺的提升, IP 的使用将进一步增加,芯片可能包含多个可编程部件(CPU 或 DSP)。为 了 SoC 设计的成功,在设计的初期探索和验证符合市场需求的最优化系统架构变得越来越重要。 AndESLive 为设计者提供了创建基于 TLM 的虚拟原型平台功能。工程师可以通过Virtual SoC Builder 快速组装基于 Andes core 的虚拟原型;通过模拟器仿真验证系统结构方案功能的完整性;通过分析功能(profiling)不断调正原型平台中各个模块的特性,在性能、功耗和芯片制造成本之间寻求最佳平衡点。 图3为使用 AndESLive 实现系统性能最优化设计的示意图。设计者首先在 VirtualSoC Builder 中建立目标 SoC 原型(图右侧上方白色框所示),然后在 VEP 的模拟器上运行测试程序验证系统性能。如果测试结果未满足规格要求,工程师可以借助模拟器产生的分析报告(图右侧下方白色框所示)快速定位系统瓶颈,并对 CPU 速度、Cache大小、总线利用率、Memory 大小等多方面进行调整后再测试,直到结果符合设计规格的要求。此时,设计者便获得了最佳的系统架构方案。

图 2 VEP 模型结构图 如果需要添加新的 VEP 模块,工程师需要进行 VEP 模型的建模。建模有两种方式,如果 SID 组件是由 C/C++语言来描述,那组件外部需要一层 XML 语言实现的描述符来进行包装;如果工程师希望用 SystemC 实现模块,则需要实现一个 SID-SystemC 桥文件,用 来 完 成 SID 与 SystemC 接 口 之 间 的 通 信 功 能 。 对 于 编 写 组 件 描 述 符 文 件 或 者SID-SystemC 桥文件,晶心科技会提供完整的培训和技术资源,帮助客户快速实现建模工作。5.使用 AndESLive 进行设计和开发5.1 探索最优化的系?架构 随着 SoC 芯片规模扩大、工艺的提升, IP 的使用将进一步增加,芯片可能包含多个可编程部件(CPU 或 DSP)。为 了 SoC 设计的成功,在设计的初期探索和验证符合市场需求的最优化系统架构变得越来越重要。 AndESLive 为设计者提供了创建基于 TLM 的虚拟原型平台功能。工程师可以通过Virtual SoC Builder 快速组装基于 Andes core 的虚拟原型;通过模拟器仿真验证系统结构方案功能的完整性;通过分析功能(profiling)不断调正原型平台中各个模块的特性,在性能、功耗和芯片制造成本之间寻求最佳平衡点。 图3为使用 AndESLive 实现系统性能最优化设计的示意图。设计者首先在 VirtualSoC Builder 中建立目标 SoC 原型(图右侧上方白色框所示),然后在 VEP 的模拟器上运行测试程序验证系统性能。如果测试结果未满足规格要求,工程师可以借助模拟器产生的分析报告(图右侧下方白色框所示)快速定位系统瓶颈,并对 CPU 速度、Cache大小、总线利用率、Memory 大小等多方面进行调整后再测试,直到结果符合设计规格的要求。此时,设计者便获得了最佳的系统架构方案。 图 3 用 AndESLive 探索最优化的系统架构5.2 大幅度缩短开?周期 在 SoC 设计中,系统性能不仅取决于芯片硬件,还取决于运行在芯片上的嵌入式软件。采用传统设计流程,设计者无法准确估算软件性能,因此就无法确定整个系统的最终规格,只能凭借工程师的经验设计。此外,软件的设计、开发也只能在芯片的硬件原型已经提供后才能执行,这使得软/硬件整合时间被推迟,于是整个系统开发周期就变长了。 AndESLive 提供了事物处理级的虚拟原型平台,即 VEP。有了和实际硬件一致的模型,软件工程师就可以和硬件设计人员并行工作,进行代码编写并在虚拟原型上进行测试。VEP 中的 TLM 模型比同等的 RTL 模型运行速度快 100 至 1000 倍,这个速度足以运行相当大的应用程序,例如像 Linux 这样的操作系统。另外,软件开发人员的提早介入,使软/硬件的集成和验证变得更加容易。这样,在芯片硬件开发完成后,大部分或者全部软件都已经准备好并经过验证,从而缩短了最后的硬件和软件集成的时间。

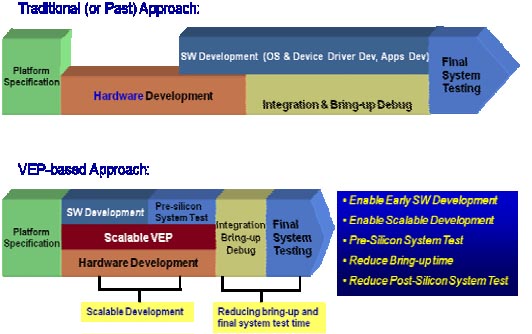

图 3 用 AndESLive 探索最优化的系统架构5.2 大幅度缩短开?周期 在 SoC 设计中,系统性能不仅取决于芯片硬件,还取决于运行在芯片上的嵌入式软件。采用传统设计流程,设计者无法准确估算软件性能,因此就无法确定整个系统的最终规格,只能凭借工程师的经验设计。此外,软件的设计、开发也只能在芯片的硬件原型已经提供后才能执行,这使得软/硬件整合时间被推迟,于是整个系统开发周期就变长了。 AndESLive 提供了事物处理级的虚拟原型平台,即 VEP。有了和实际硬件一致的模型,软件工程师就可以和硬件设计人员并行工作,进行代码编写并在虚拟原型上进行测试。VEP 中的 TLM 模型比同等的 RTL 模型运行速度快 100 至 1000 倍,这个速度足以运行相当大的应用程序,例如像 Linux 这样的操作系统。另外,软件开发人员的提早介入,使软/硬件的集成和验证变得更加容易。这样,在芯片硬件开发完成后,大部分或者全部软件都已经准备好并经过验证,从而缩短了最后的硬件和软件集成的时间。 图 4 传统设计流程与基于 VEP 的设计流程 采用基于 AndESLive VEP 的开发流程与传统开发流程相比(图 4 所示),软/硬件开发可以同时进行,因此系统的设计、开发和验证过程更加快速,这不仅使得产品可以更早的进入市场,而且各种开发资源也得到了更大的使用效率,从而进一步降低了成本。6. 结语晶心科技(Andes)是一家致力于32位嵌入式处理器IP的授权公司,面对不同应用层级的32位处理器市场,推出了Andes core:N9(50-200MHz)、N10(50-240MHz)、N12(50-660MHz)三个系列的低功耗高性价比的32位处理器软、硬核IP。AndESLive是晶心科技为基于Andes core进行SoC开发而设计的ESL开发工具。AndESLive帮助客户找到最优化的系统架构方案,使产品更有效的满足市场需求;基于VEP的设计流程,大幅缩减了芯片开发周期,使产品在市场中具备更强的竞争力。

图 4 传统设计流程与基于 VEP 的设计流程 采用基于 AndESLive VEP 的开发流程与传统开发流程相比(图 4 所示),软/硬件开发可以同时进行,因此系统的设计、开发和验证过程更加快速,这不仅使得产品可以更早的进入市场,而且各种开发资源也得到了更大的使用效率,从而进一步降低了成本。6. 结语晶心科技(Andes)是一家致力于32位嵌入式处理器IP的授权公司,面对不同应用层级的32位处理器市场,推出了Andes core:N9(50-200MHz)、N10(50-240MHz)、N12(50-660MHz)三个系列的低功耗高性价比的32位处理器软、硬核IP。AndESLive是晶心科技为基于Andes core进行SoC开发而设计的ESL开发工具。AndESLive帮助客户找到最优化的系统架构方案,使产品更有效的满足市场需求;基于VEP的设计流程,大幅缩减了芯片开发周期,使产品在市场中具备更强的竞争力。

查看评论 回复