Verilog HDL 模块和端口以及门级建模 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-07

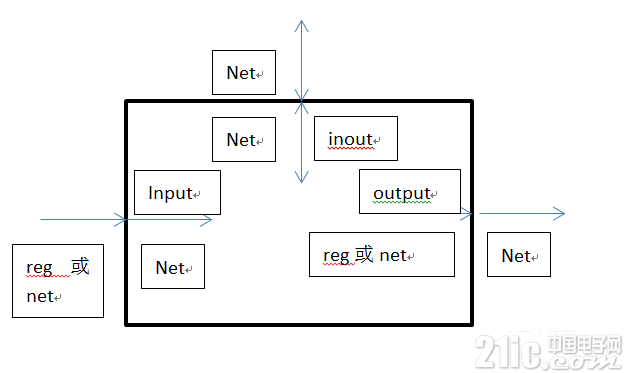

[导读]模块定义以关键字module开始,模块名、端口列表、端口声明和可选的参数声明必须出现在其他部分的前面,模块内部5个组成部分:变量声明、数据流语句、底层模块实例、行为语句块以及任务和函数。

模块定义以关键字module开始,模块名、端口列表、端口声明和可选的参数声明必须出现在其他部分的前面,模块内部5个组成部分:变量声明、数据流语句、底层模块实例、行为语句块以及任务和函数。

本文引用地址: http://www.21ic.com/app/eda/201702/704701.htm

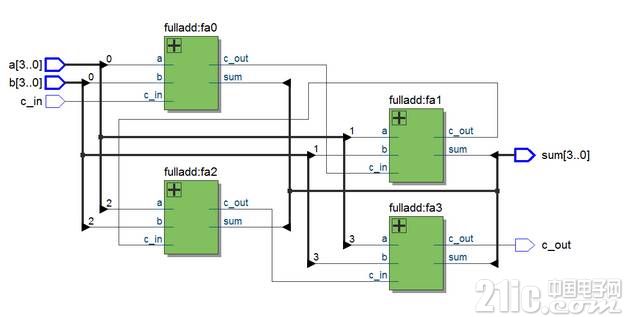

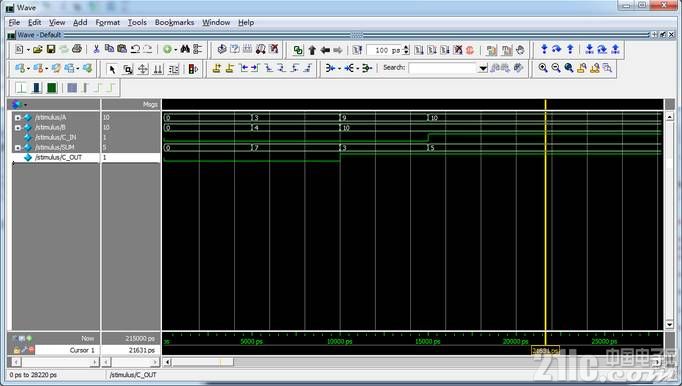

门级建模 以一个四位脉动进位全加器为例,它由四个一位全加器组成,一位全加器的数学表示如下:sum=(a⊕b⊕cin) cout=(a·b)+cin·(a⊕b)。

查看评论 回复