前仿真和后仿真 -

[导读]作者:李秋凤,华清远见嵌入式学院讲师。

仿真可以分为前仿真和后仿真,前仿真是功能仿真,目标是分析电路的逻辑关系的正确性,仿真速度快,可以根据需要观察电路输入输出端口和电路内部任一信号和寄存器的波形,后

作者:李秋凤,华清远见嵌入式学院讲师。

仿真可以分为前仿真和后仿真,前仿真是功能仿真,目标是分析电路的逻辑关系的正确性,仿真速度快,可以根据需要观察电路输入输出端口和电路内部任一信号和寄存器的波形,后仿真是将电路的门延迟参数和各种电路单元之间的连线情况考虑在内后进行仿真,得到的仿真结果接近真实的应用情况,后仿真的速度相对于前仿真慢得多,在观测内部节点波形时比较困难,在一个完整的电路设计中应该包括这两个过程。

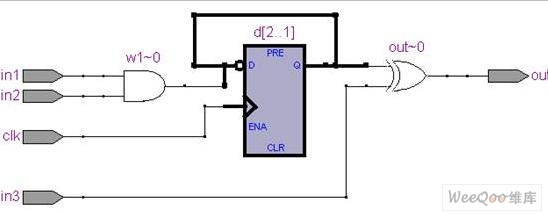

下面是简单的数字电路,代码及综合后的RTL网表如下:

`timescale 1ns/1ps

module ml(clk,in1,in2,in3,out);

input clk;

input in1,in2,in3;

output out;

wire w1,w2;

reg d1,d2;

assign w1=~(in1&in2);

always@(posedge clk)

d1<=w1;

assign w2=~d1;

always@(posedge clk)

d2<=w2;

assign ut= d2^in3;

endmodule

分析上面代码可以看出,上面只是反映的是逻辑功能,实际上,每个门电路都有工作延时,如果考虑到工作延时,则代码需要进行修改,修改后的代码更能反映电路的实际工作情况

`timescale 1ns/1ps

module ml(clk,in1,in2,in3,out);

input clk;

input in1,in2,in3;

output out;

wire w1,w2;

reg d1,d2;

parameter delay1=1,delay2=2;

assign # delay1 w1=~(in1&in2);

always@(posedge clk)

d1<= # delay2 w1;

assign # delay1 w2=~d1;

always@(posedge clk)

d2<= # delay2 w2;

assign # delay1 ut= d2^in3;

endmodule

这段代码中定义了两个延时参数,分别对应组合逻辑的门延时和寄存器的传输延时,这里的延时与真正的门延时在具体数值上是不同的,但是这种每次赋值操作时都加入延时的方法有助于对电路后仿真时可能的延时情况给出定性分析的结果。

“本文由华清远见http://www.embedu.org/index.htm提供”

来源:华清远见0次

查看评论 回复