基于Multisim的数字时钟设计 -

[导读]作者:刘允峰

加强实验教学、提高动手能力与创新能力是高等教育的教学重点。伴随着电子技术的快速发展,元器件、设备仪器不断更新,现有的实验室条件无法满足各种电路设计、调试要求,尤其综合性、创新性实验需要

作者:刘允峰

加强实验教学、提高动手能力与创新能力是高等教育的教学重点。伴随着电子技术的快速发展,元器件、设备仪器不断更新,现有的实验室条件无法满足各种电路设计、调试要求,尤其综合性、创新性实验需要多种仪器共同完成其功能,暴露出实验室仪器设备费用高、损耗大、更新慢的缺点,一般高校无法满足此类实验要求。电路仿真软件Multisim拥有庞大的元器件库,具有强大的虚拟仪器功能,有一般实验室少有的频谱分析仪、网络分析仪等虚拟仪器。在电子技术基础实验中引入Multisim,再配合传统的实验设备进行实验,减轻了购买、更新实验设备的资金压力。可以说,利用虚拟仪器技术进行实验教学已经势在必行。有些院校已经使用Multisim展开教学。

1 数字时钟实验

数字时钟实验是电子技术基础实验中的综合性实验之一。数字时钟是一种典型的数字电路,包括了组合逻辑电路和时序逻辑电路,通过设计数字时钟,学生会进一步了解数字时钟的原理和集成电路的使用方法,加深掌握逻辑电路的原理和使用方法。

1.1 数字时钟的组成

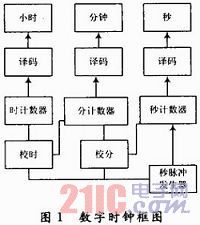

数字时钟是一个对标准频率(1 Hz)进行计数的计数电路。在计数时,如果起始时间和当前时间不一致,还需要加一个校时电路。同时,校时电路还可以在调试数字时钟时发挥重要作用。数字时钟构成如图1所示。

1.2 模60和模24计数器的实现

“秒”和“分”计数器都是模60计数器,由个位的10进制计数器和十位的6进制计数器组成。74LS90是10进制计数器,利用2片74LS90,通过异步清零功能,并配合与门74LS08使用,实现模60计数器或模24计数器的功能。

1.3 译码电路

译码电路可以选用4线-7段译码器/驱动器74LS248,采用共阴极LED数码显示器。

1.4 校时电路

当数字时钟接通电源或计时出现误差时,需要校准。常用的校准方法为“快速校准法”,即校准的时候使分、时计数器对1 Hz的秒脉冲信号进行计数。

2 仿真、测试

实验环境:Multisim10.1,Windows XP。经实际测试,60进制和24进制计数器都能够运行正常,能够实现60进制和24进制的逻辑功能,校时电路也能够对时、分计数器进行校正。实现了数字时钟的功能。

仿真电路如图2所示。

3 结语

使用Multisim仿真数字时钟时,如果按照现实中的时、分来计时的话,不便于观察时钟运行周期。比如,花费一天的时间才能观察24小时的显示周期是否正确。而提高输入脉冲的频率,可以“缩短”时间,实验者可以花费较少的时间观察时钟运行周期的变化。运行环境是CPU AMD Athlon 2.01 GHz,仿真脉冲最高频率达到240 MHz,再高的频率就影响LED的显示,无法清晰观察时钟的变化。数字时钟的实验还能做一些功能扩展,如整点报时、定时控制,可以留做大学生创新性实验的一部分。通过制作数字时钟,即加深了理论知识的学习,还锻炼了动手能力和创新能力。先利用Multisim仿真,再用实际器件搭建电路,实现逻辑功能,一方面节省了器件费用、减少了仪器损耗,另一方面,提高了工作效率。因此,利用Multisim强大的功能对电子电路进行仿真测试,参数精确可靠,可以提高电路的设计和分析效率。

查看评论 回复

"基于Multisim的数字时钟设计 -"的相关文章

- 上一篇:如何选择封装形式 -

- 下一篇:布线的设计技巧 -