编译和布线 - HDL语言及源代码 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

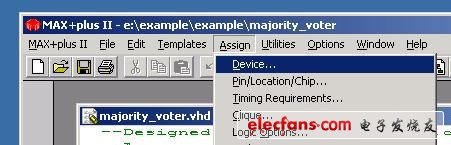

我们先要指定所用芯片的型号,

菜单:Assign->Device

如下图

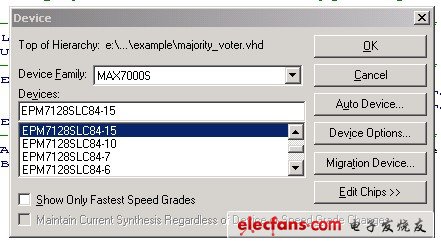

将弹出一窗口

(注意把show only fastest speed grades前的钩去掉,否则看不到EPM7128SLC84-15)

在Debice Family 中选择MAX7000S

DEVICE选择EPM7128SLC84-15

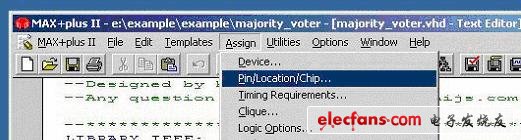

再指定芯片的管脚(也就是把你设计的IO口如L1,L2指定到芯片对应的管脚上如10,9)

Assign->Pin/LocaTIon/Chip(也可以在空白处点右键,选Assign->Pin/LocaTIon/Chip)

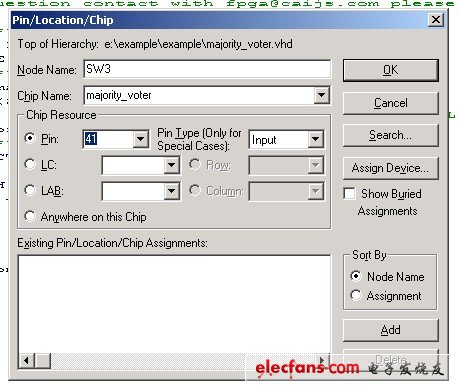

将弹出下图窗口:

在Node Name 中添入SW3

Chip Resource 下的Pin中输入管脚41

在Pin type中输入input

点ADD