FPGA最小系统电路分析:高速SDRAM存储器接口电路设计 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-05

[导读]高速SDRAM存储器接口电路设计SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。一般比较常用的SDRAM

高速SDRAM存储器接口电路设计

本文引用地址: http://www.21ic.com/app/eda/201308/188605.htm

SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。

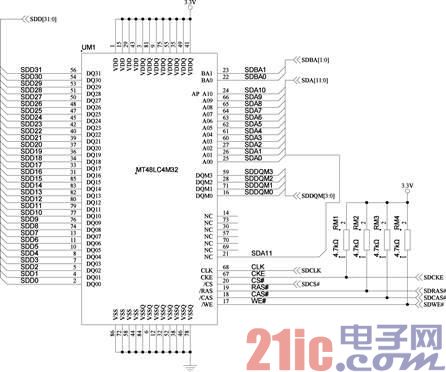

一般比较常用的SDRAM包括现代HY57V系列、三星K4S系列和美光MT48LC系列。例如,4M×32位的SDRAM,现代公司的芯片型号为HY57V283220,三星公司的为K4S283232,美光公司的为MT48LC4M32。这几个型号的芯片可以相互替换。SDRAM典型电路如图2.9所示。

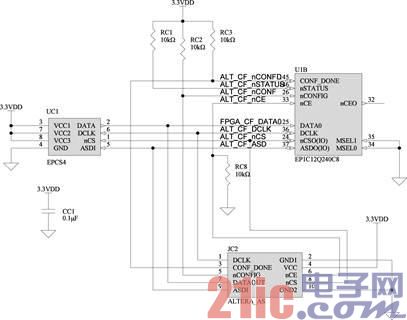

图2.8 AS模式原理图

图2.9 SDRAM典型电路

查看评论 回复